Gidel FPGA ProcDev Dev Kit including ProcWizard | Gidel FPGA IP Cores | Gidel I++ HLS Application Support

Gidel ProcDev FPGA Development Kit including ProcWizard

The Gidel Proc Developer’s Kit (ProcDev Kit) is an easy to use FPGA design tool. It optimises on-board memory and host communication in support of your algorithm implementation on the FPGA.

The Developer’s kit includes the ProcWizard application, an API, Gidel IPs, examples, and HDL and software libraries.

ProcWizard Rapid FPGA Application Development Tool

The Gidel ProcWizard™ is a hardware–software integration tool that simplifies FPGA project development. ProcWizard enables rapid design of applications intended to run on Gidel FPGA boards.

The design is automatically translated into HDL and C++ code. The generated HDL and C++ code communicate over the PCIe bus for easy integration of the hardware and software.

ProcWizard can also be used to test and debug designs on your PC. In Debug Mode, you can access the Gidel “Proc” FPGA board via a structural inspector, either manually or by using macros and scripts.

Hardware and software designers can cooperate using the same information and project definitions. Working in parallel in the Gidel ProcWizard shared environment, development time is reduced, product reliability is increased, and maintainability is improved.

ProcWizard’s main features include:

- Automatic integration of software and Gidel’s “Proc”-series FPGA boards

- Automatic integration of Gidel’s IP cores into the design

- C++ class application driver generation

- HDL code generation (top-level design, PCI interface sub-design, board constraints)

- Documentation generation (HTML or Microsoft Word style)

- Certification of partition generation

- Simple, easy-to-use menu-driven interface

- Automatic hardware initialization and clock setting

- Automatic FPGA loading

- Automatic DMA manipulations

- Hardware debugging

Gidel FPGA Intellectual Property IP Cores

The Gidel “ProcDev” Developer’s kit includes a set of IPs for simplifying and enhancing development tasks.

MultiPort FPGA IP Core

The Gidel MultiPort IP is a memory controller that optimizes on-board memory according to application data flow needs. This controller enables parallel access from up to 16 independent ports per memory bank. Each port may belong to a separate logical memory. All ports are connected to the same memory domain and can be accessed independently or simultaneously, with individual clock domains and data widths.

MegaFIFO FPGA IP Core

The MegaFIFO allows simple and convenient data transfer between the FPGA board memory banks and the FPGA logic and or the PC host.

MegaDelay FPGA IP Core

The MegaDelay IP allows high-bandwidth delays to optimize streaming applications. This IP may significantly reduce memory access requirements, when combined with the FPGA’s internal memory and logic.

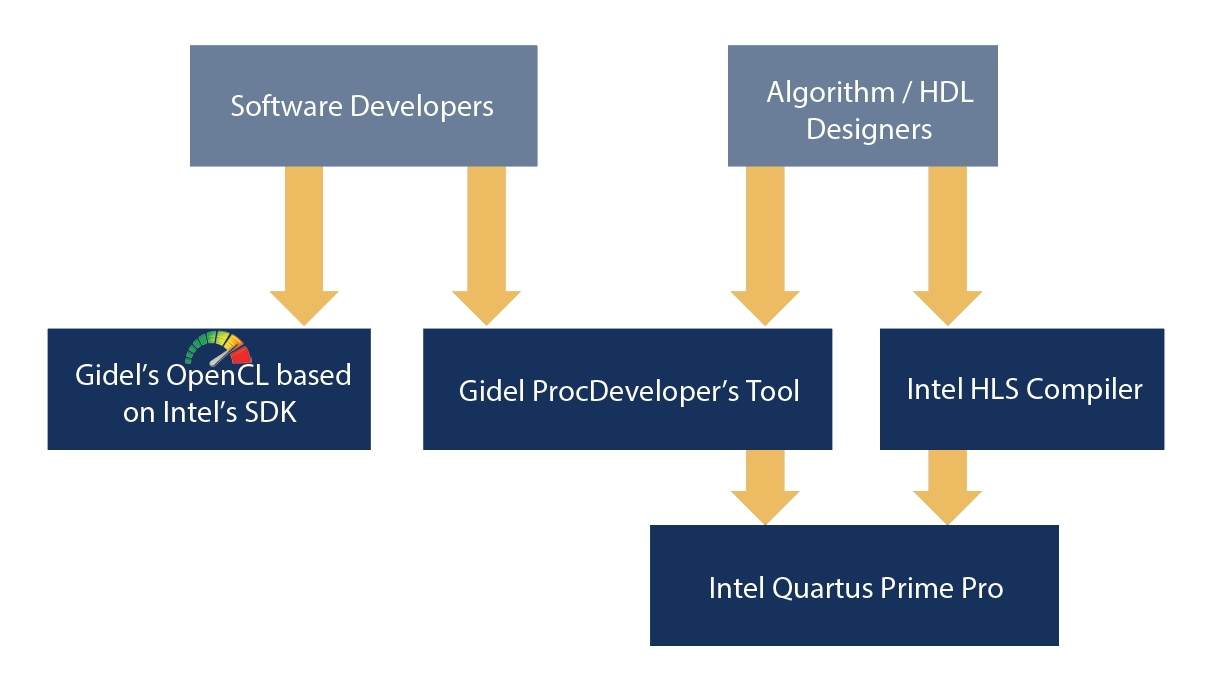

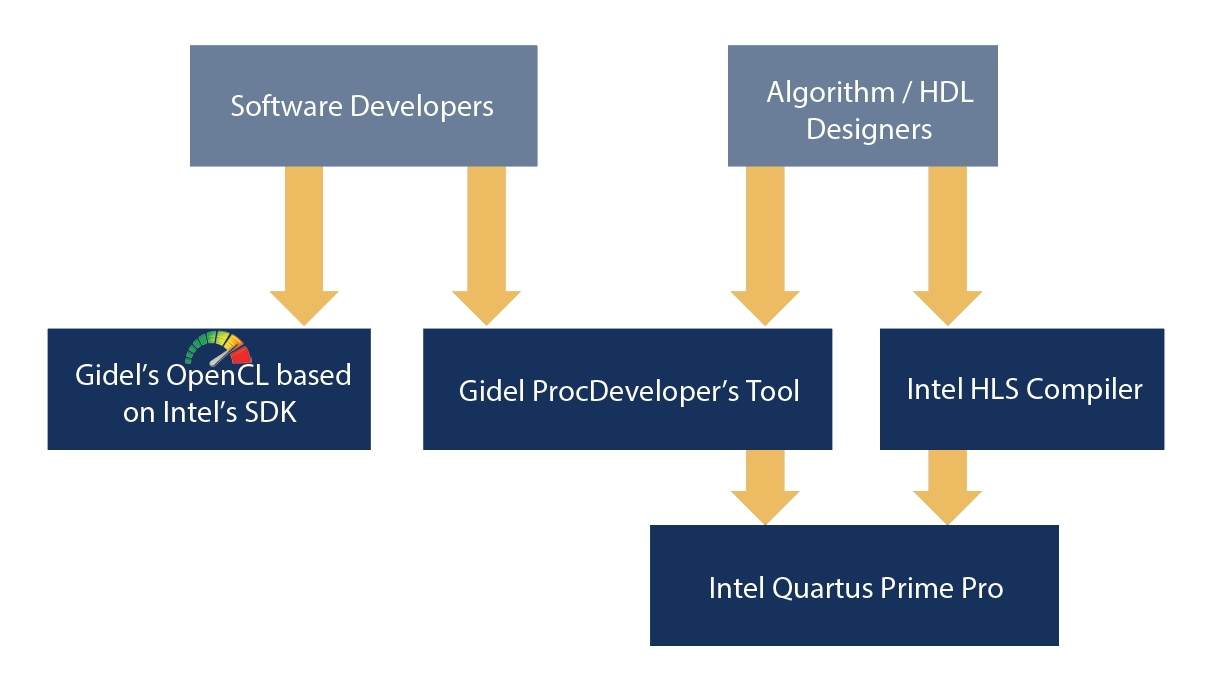

Gidel I++ HLS Application Support Package

HLS Application Support Package (I++) enables the use of Intel’s High Level Synthesis (HLS) tool, which takes C++ as input and generates FPGA-optimized Register Transfer Level (RTL). The significant code reduction reduces the RTL verification time.

Product Data